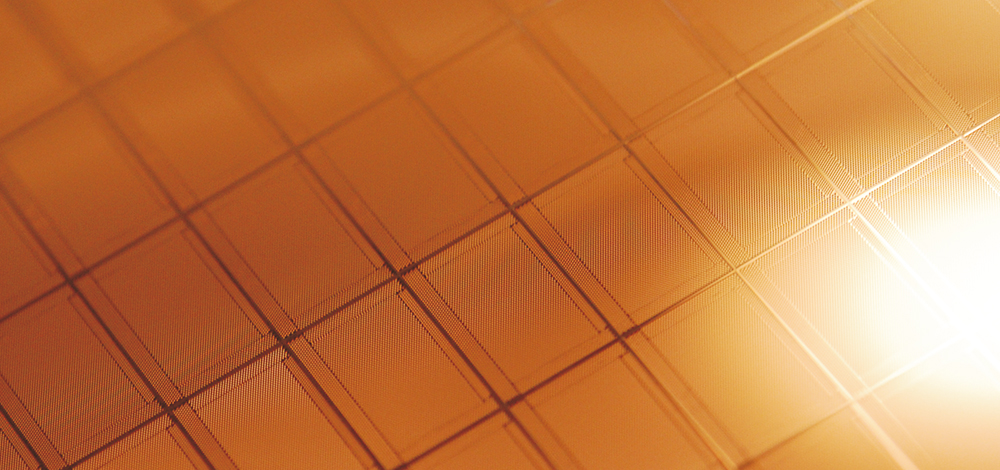

Wafer Metallisierung

Die Verwendung von Kupfer als Leitungsmaterial in der Halbleiterindustrie revolutionierte den Metallisierungsprozess und trug wesentlich dazu bei schnellere, kleinere und weniger Energie verbrauchende Prozessoren und integrierte Schaltungen zu ermöglichen. Neue Prozesstechnologien ermöglichten komplexere und mehrschichtige Verbindungen, zusammen mit den elektrischen Eigenschaften von Kupfer führte dies zu einer enormen Leistungsteigerung der Prozessoren.

Im Fraunhofer IPMS werden der ECD-Prozess und das Kupfermaterial ständig optimiert, um hohe Leistungen und Signalübertragung bei geringem Energiebedarf in Verbindung mit langer Lebensdauer zu garantieren. Um dies zu gewährleisten, wird der ECD-Prozess für die galvanische Abscheidung von Metallschichten durch Elektrolyt-Screening, Badstandzeiten-Untersuchung und Prozesscharakterisierung untersucht. Elektrochemische Messverfahren und umfangreiche Analysen sind verfügbar um Kupfer-Superfillings zu studieren.

Unsere Anwendungsbereiche

- 28 nm Technologieknoten und darunter

- 300 mm/12 in wafer & beaker tests

- Dual damascene plating

- Bump plating

- TSV plating

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme