Wafer Cleaning

Da die Anforderungen an eine erhöhte Bauelementleistung und -zuverlässigkeit in der VLSI- und ULSI-Silizium-Schaltungstechnik immer anspruchsvoller geworden sind, sind Techniken zur Vermeidung von Verunreinigungen und Verfahren zur Erzeugung sehr sauberer Wafer-Oberflächen von entscheidender Bedeutung. Zahlreiche Reinigungsvorgänge sind im Verlauf der Halbleiterfertigung notwendig und müssen bei bestimmten kritischen Prozessschritten durchgeführt werden. Um eine schnelle, selektive, gleichmäßige und kosteneffektive Reinigung zu gewährleisten, bietet das Zentrum für Nanoelektronische Technologien eine hochmoderne Reinigungsplattform.

Als Bindeglied und Testumgebung von Zulieferern und Chipherstellern bieten wir Evaluierung, Screening und Optimierung von neuen Chemikalien und Prozessen vom Labormaßstab bis hin zum Test auf eigenen Wafern (2x nm Technologieknoten) an.

Unsere Leistungen

- Post Etch Residues Removal (PERR)

- Photoresist stripping & Lithographie-stack-rework

- Benchmarking von Verbrauchsmaterialien

- Langzeittests / Ergiebigkeitstests

- Post CMP clean (Chemie und Verbrauchsmaterialien)

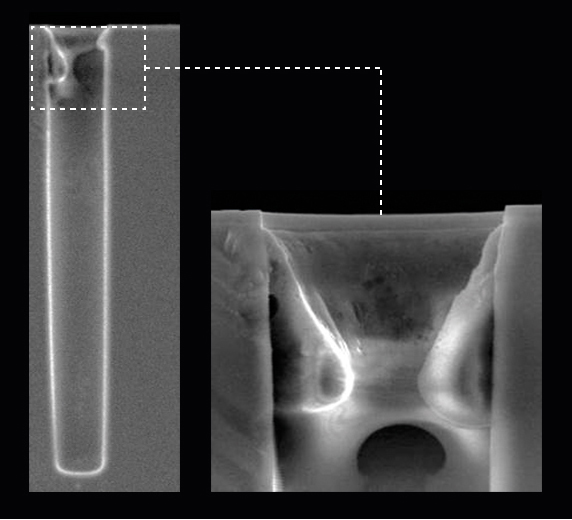

- Entfernung von polymeren Rückständen nach TSV-Etch

- Dual Damascene Hartmasken-Etch

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme