Nanopatterning / E-Beam Lithography

Die Herstellung von Strukturen im Nanomaßstab ist für eine Vielzahl von Anwendungen in der Halbleiterindustrie von entscheidender Bedeutung. Zentrale Herausforderungen sind die Erzeugung präzise kontrollierter Strukturen mit kleinen Abmessungen, die flexible und anpassungsfähige Layouterstellung und Prozesse sowie die einheitliche und reproduzierbare Integration auf Waferebene.

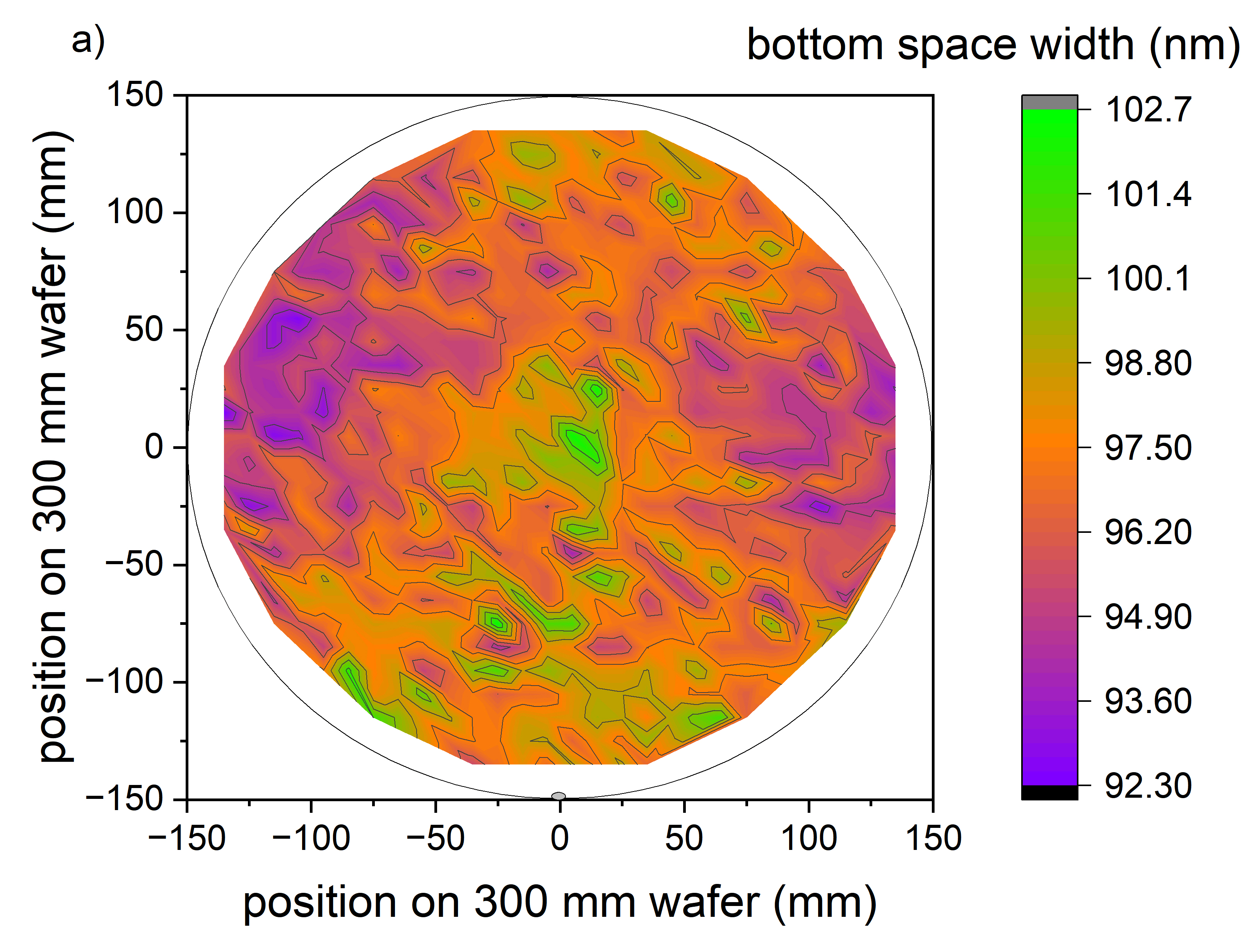

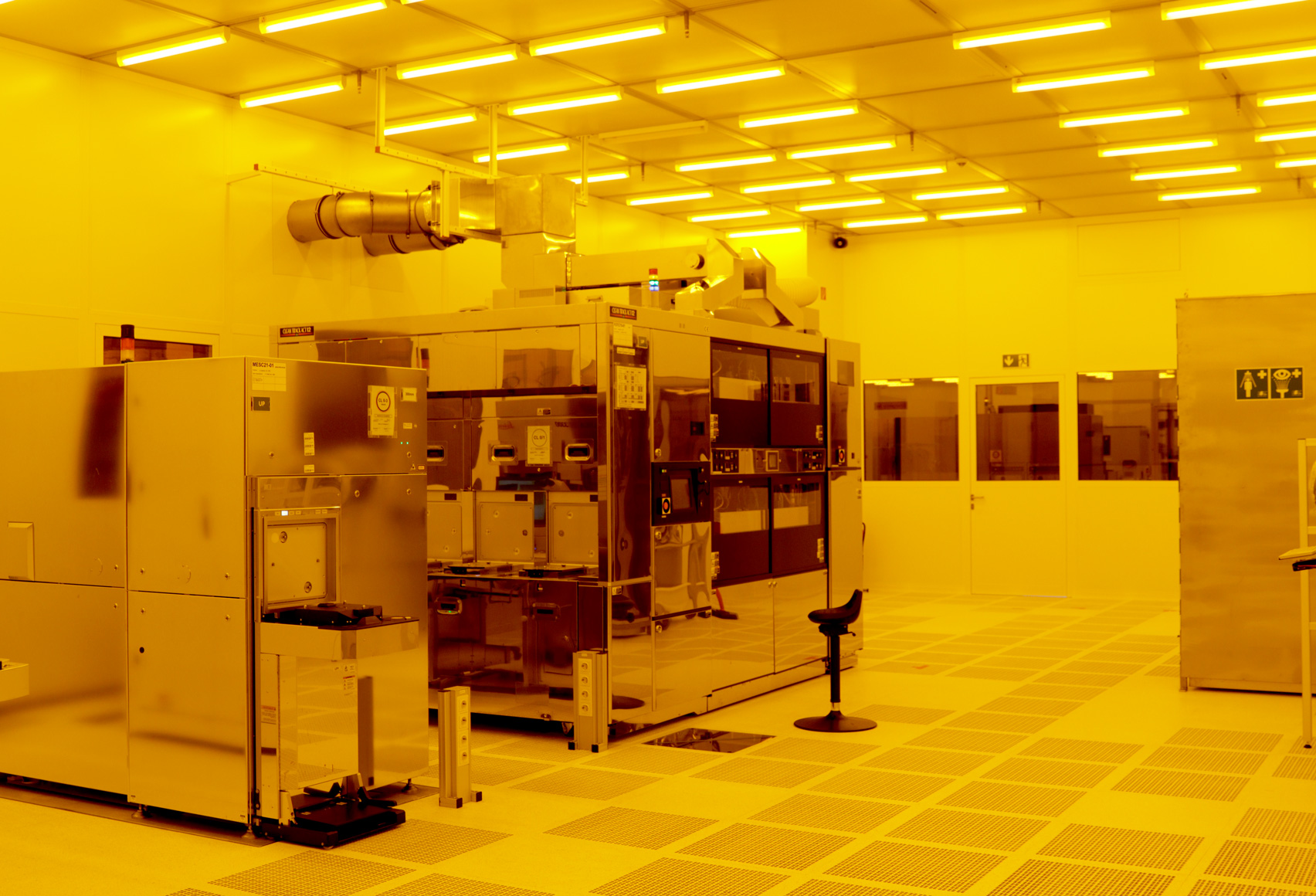

Das Fraunhofer IPMS bietet modernste Möglichkeiten der Nanostrukturierung mittels Elektronenstrahl-Direktschreiblithographie und reaktivem Ionenätzen. So können kundenspezifische Strukturen mit Größen unter 40 nm auf einer Vielzahl von Wafergrößen und Substrattypen erzeugt werden. Ausgehend vom Design des Kunden wird das gesamte Paket von der Layouterstellung und -modifikation, der Datenaufbereitung, der Elektronenstrahllithographie, der Musterübertragung mittels Ätzverfahren zusammen mit der Inline-Messtechnik und Analytik bis hin zum Dicing in einzelne Chips angeboten.

Anwendungsbeispiele

- Fabrikation von Teststrukturen für die Technologieentwicklung

- Strukturierung von anwendungsspezifischen integrierten Schaltungen (ASICS)

- Designtests von innovativen Bauelementen und Zellkonzepten und deren Variation auf einem Wafer (Chip Shuttle)

- Kalibriermuster für die Metrologieentwicklung

- MEMS- und NEMS-Strukturierung mit produktiver Qualität

- „Mix & Match“ mit optischen Belichtungstechniken

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme