Halbleiter-Technologiemodule für Quantencomputing, KI und Internet-of-Things (TO.QI)

Projektlaufzeit: 2024 - 2027

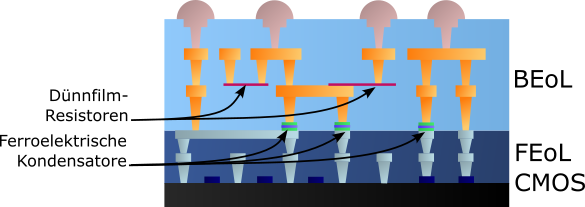

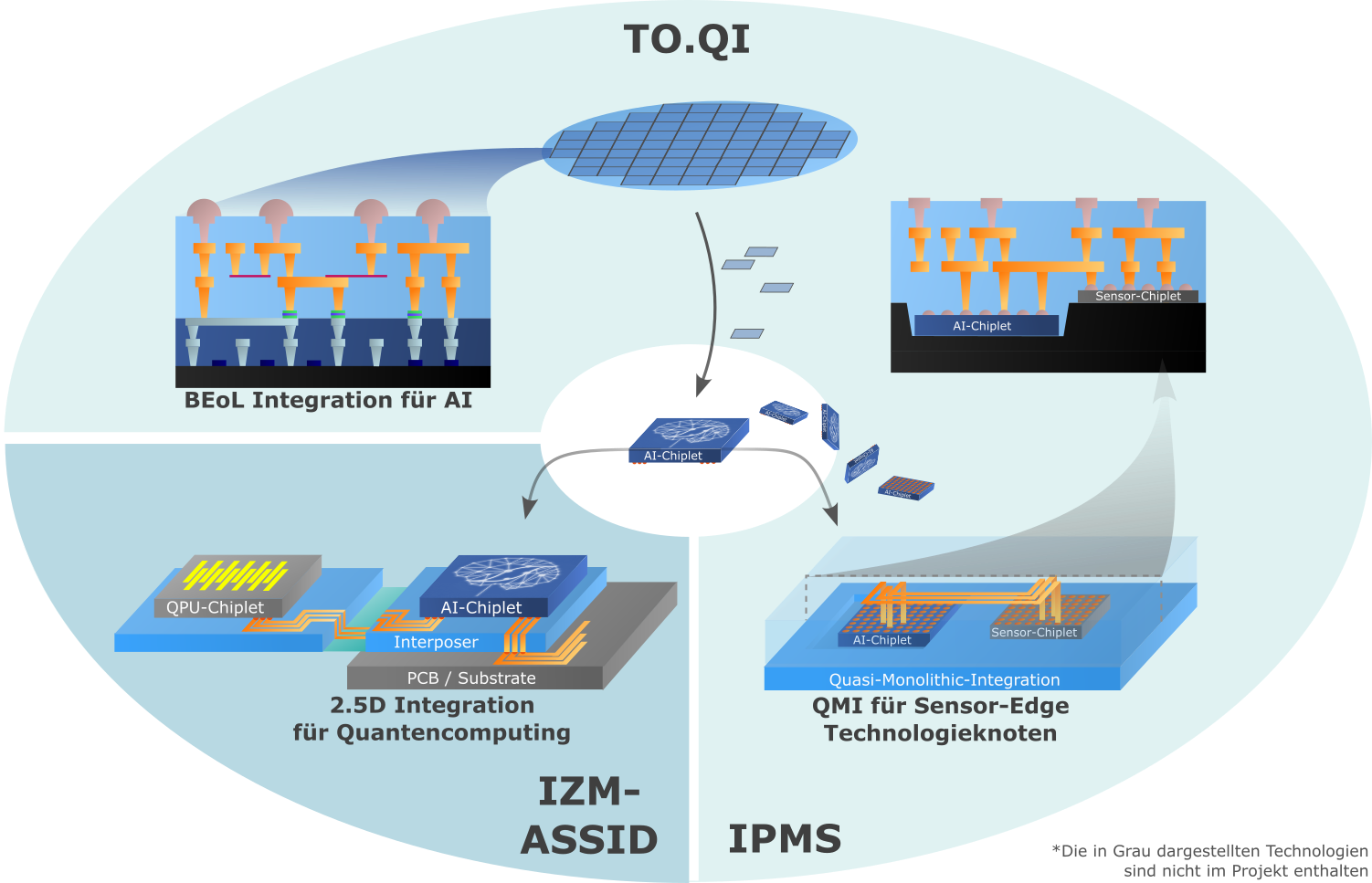

Der rasant wachsende Bedarf an Rechenleistung, gerade im Bezug auf Quantencomputing, Künstliche Intelligenz und "Internet der Dinge" (IoT) Anwendungen, erfordert zwingend neue Mikroelektronik-Lösungen, um dem damit einhergehenden, drastisch zunehmenden Energieverbrauch entgegenzuwirken und die Treibhausgas-Emissionen zu senken. Ein vielversprechender Lösungsansatz hierfür sind neue Rechenarchitekturen basierend auf nicht-flüchtigen Speicherbauelementen, welche Compute-in-Memory / neuromorphes Computing ermöglichen, sowie die möglichst kompakte Integration verschiedener Systeme. Letzteres kann durch Heterointegration erreicht werden. Dabei sind die 3D Integration via eines Interposers oder die Quasi-monolithische Integration mehrerer Chiplets besonders vielversprechend für Quantencomputing-Systeme und IoT-Sensor-Edge-Lösungen.

Ziel des Projekts TO.QI ist daher die Entwicklung solcher Technologiemodule, welche eine forschungsnahe Pilotfertigung von neuen Bauelementen und Heterointegrationsmethoden ermöglichen soll. Entsprechend gliedert sich das Projekt in drei Abschnitte, wobei zwei Technologiemodule vom Fraunhofer IPMS entwickelt werden und ein Technologiemodul vom Fraunhofer IZM-ASSID.

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme