In der heute üblichen Transistorfertigung werden die Einzelbauelemente durch gezielt hergestellte tiefe Gräben von isolierendem Siliziumoxid elektrisch voneinander getrennt. Um die Dimension der Isolationsgräben nanometergenau anzupassen, ist ein chemisch mechanischer Planarisierungsprozess (CMP) erforderlich. Heute wird bei diesem Schritt mit einer Poliersuspension (Slurry) basierend auf Ceroxid-Abrasivpartikeln gearbeitet. Da es sich bei Cer um ein Element der Seltenen Erden handelt, dessen Oxid im Verdacht steht, krebserregend zu sein, laufen am Fraunhofer IPMS Versuche mit umweltverträglicheren alternativen Slurries auf Siliziumoxidbasis.

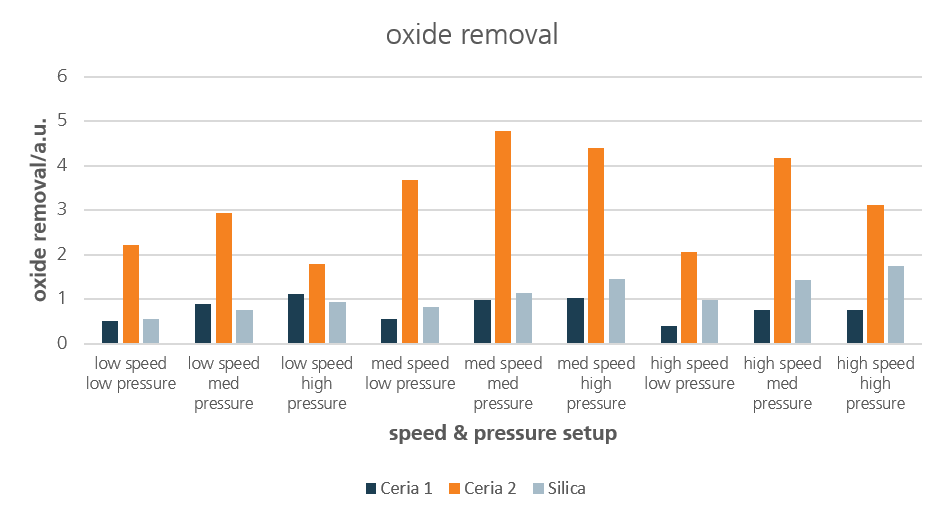

Da beim Fertigungsprozess Siliziumoxid abgetragen wird und die Topographie mit Hilfe einer Polierstoppschicht aus Siliziumnitrid eingestellt wird, sind (mindestens) zwei Parameter zur Bewertung einer Slurry von zentraler Bedeutung: Der Oxidabtrag sollte hinreichend hoch sein, um einen hohen Prozessdurchsatz zu ermöglichen. Eine hohe Selektivität des Abtrags ist erforderlich, um den Prozess bei Erreichen der Polierstoppschicht zu beenden.

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme