QSolid - Quantum computer in the solid state

Projektlaufzeit: 2021 - 2026

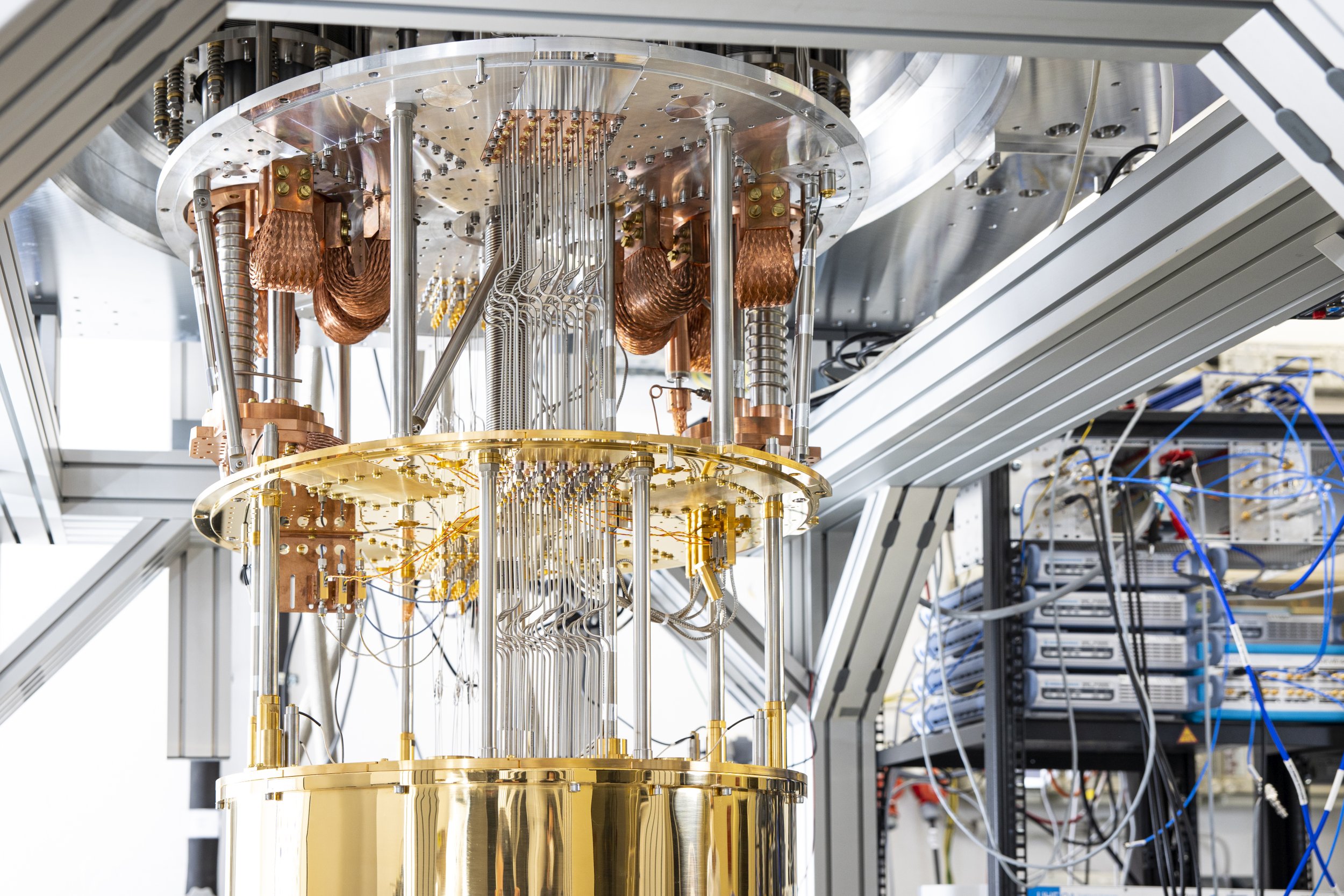

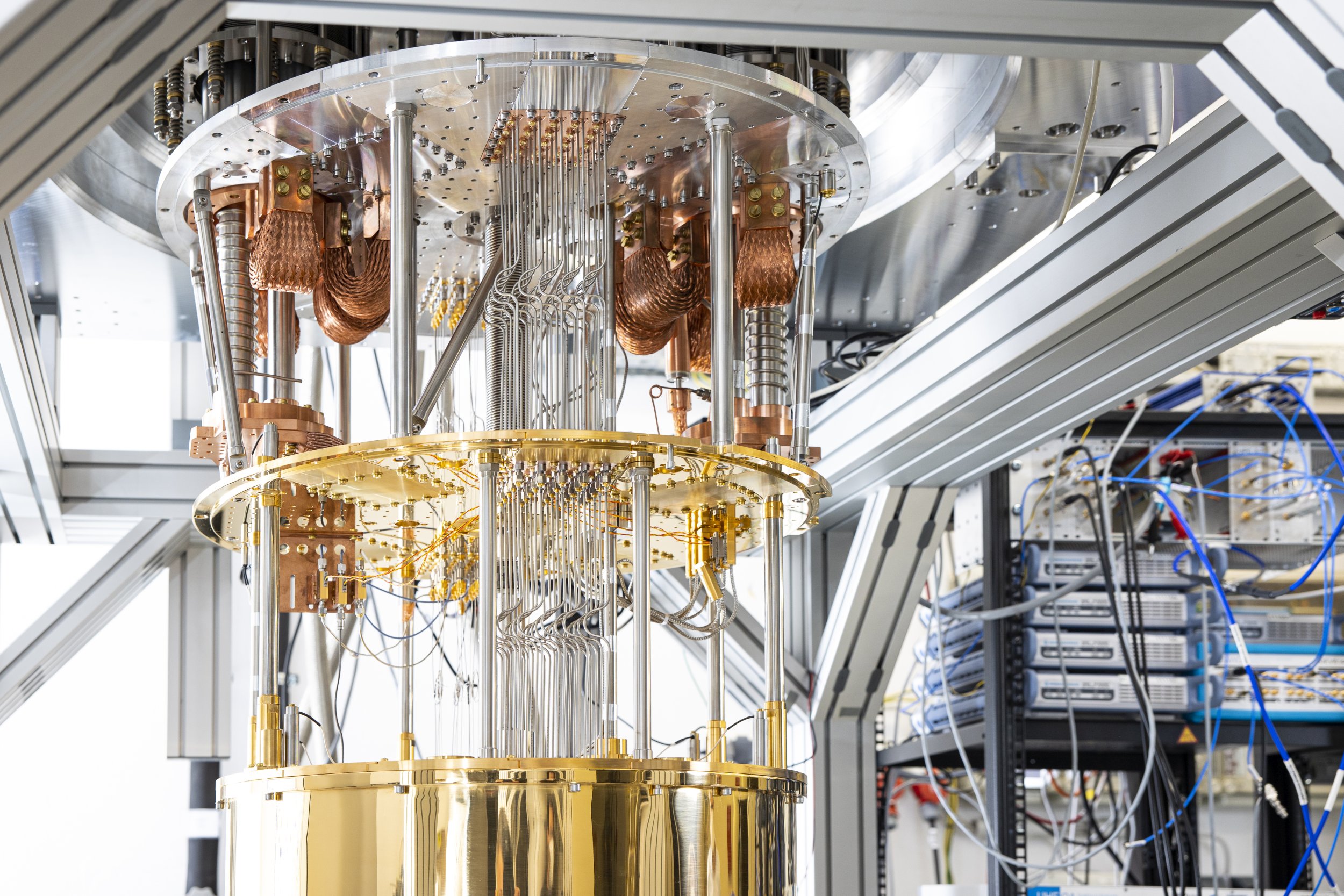

Der Bau eines kompletten Quantenrechners basierend auf Spitzentechnologie aus Deutschland, das ist das Ziel des Verbundprojekts QSolid. Gemeinsam mit 24 deutschen Forschungseinrichtungen und Unternehmen und unter Koordination des Forschungszentrums (FZ) Jülich arbeitet das Fraunhofer IPMS an einem Quantencomputer mit verbesserten Fehlerraten. Ziel ist es, Deutschland auf dem Gebiet der Quantentechnologie an die Weltspitze zu bringen und zahlreiche neue Anwendungen für Wissenschaft und Industrie zu erschließen. Der erste Demonstrator wird Mitte 2024 in Betrieb gehen und es ermöglichen, Anwendungen sowie Benchmarks für Industriestandards zu testen.

Im Mittelpunkt des Projekts stehen Quantenbits – kurz Qubits – von sehr hoher Qualität, d.h. mit einer geringen Fehlerrate. Vorgesehen ist ein System, das verschiedene Quantenprozessoren enthält, die auf supraleitenden Schaltkreisen mit reduzierter Fehlerrate beruhen. Der Ansatz gilt als weltweit führend und wird u. a. auch von Google, IBM und Intel verfolgt. Die Multiprozessor-Maschine des FZ Jülich soll mindestens drei unterschiedliche Quantenchips parallel betreiben: ein „Moonshot-System“, dessen Rechenleistung die klassischer Superrechner übertrifft, ein anwendungsspezifisch designtes System, das bereits für industriell nützliche Quantenberechnungen geeignet ist, sowie eine Benchmarking-Plattform, die vorrangig auf die Entwicklung digitaler Zwillinge und industrieller Standards ausgerichtet ist.

Das Fraunhofer IPMS steuert seine Expertise in der hochmodernen, industriekompatiblen CMOS-Halbleiterfertigung im 300-mm-Waferstandard bei. Damit werden skalierbare Quantenprozessoren ermöglicht, die auf den Errungenschaften und Vorteilen der siliziumbasierten Halbleiterfertigung aufbauen. Dies betrifft zum Beispiel Herstellungsprozesse wie Abscheidung und Nanostrukturierung oder die elektrische Charakterisierung im Wafermaßstab. Gemeinsam mit GLOBALFOUNDRIES und dem Fraunhofer IZM-ASSID wird eine Interposer-Technologie entwickelt, die sich auf hochdichte supraleitende Verbindungen und thermische Entkopplung durch fortschrittliches Packaging konzentriert. Zusätzlich soll die kryogene Charakterisierung der CMOS-Technologie von GLOBALFOUNDRIES für eine skalierbare Steuerung erfolgen.

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme