Chemisch-mechanisches Polieren (CMP)

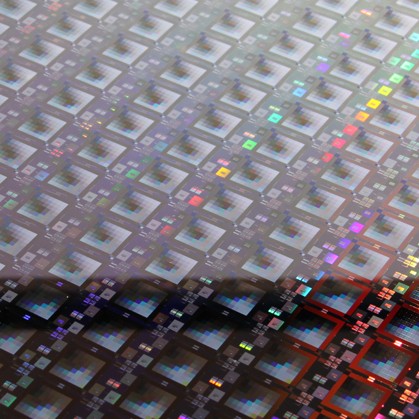

Hochintegrierte Schaltungen, wie Logik- und Speicherchips, bestehen aus vielen Materialschichten. Im Zuge der Herstellung müssen die Oberflächen immer wieder planarisiert werden, um ausreichende Prozessfenster für kritische Prozesse wie Lithographie und Ätzen zu erhalten. Weiterhin sorgt die Planarisierung für definierte Größen der Strukturen und damit letztlich für eine zuverlässige Funktion der elektronischen Elemente. Die chemisch-mechanische Planarisierung (CMP) ist der Stand der Technik, um die notwendige Planarität zu erreichen. Die kontinuierliche Verkleinerung in der Halbleitertechnologie geht einher mit einem höheren Anspruch an die Genauigkeit sowie einer höheren Anzahl der verwendeten Materialien. Daher ist es notwendig, die verschiedenen CMP-Prozesse zu verstehen und neue Prozesse für neu eingeführte Materialien zu entwickeln um die Anforderungen der kommenden Technologieknoten erfüllen zu können.

Das Fraunhofer IPMS bietet

- CMP-Prozessentwicklung und -optimierung

- CMP-Entwurf für die Entwicklung von Fertigungsstrategien für und mit den Herstellern von Halbleiterprodukten

- Screening und Charakterisierung von CMP-Verbrauchsmaterialien (Polierpad - Conditioner - Slurry - Post-CMP-Reinigungschemie - Bürste - Filter - und mehr)

- Charakterisierung des CMP-Prozesses (Planarisierung - Defektivität - Abtragsraten, Selektivität - Statische Ätzraten - Elektrische Leistung und Zuverlässigkeit)

- Modellierung und Simulation des Planarisierungsverhaltens von strukturierten Wafern

- CMP-Wafer-Verarbeitung auf Anfrage

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme